## 6.004 Tutorial Problems L08 – Combinational Devices and Introduction to Minispec

**Note:** A subset of essential problems are marked with a red star ( $\star$ ). We especially encourage you to try these out before recitation.

### Problem 1. ★

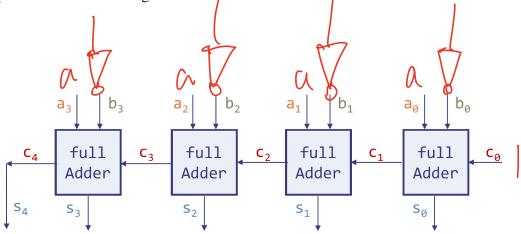

(A) Consider the 4-bit ripple carry adder we saw in lecture. Its circuit is shown below. Modify the diagram to build a **subtractor**, i.e., a circuit that given 4-bit inputs *a* and *b*, computes a - b.

You may use only one ripple-carry adder, and may add at most four gates to the diagram. Assume that a and b use two's complement representation. Your circuit should return the result in two's complement representation.

*Hint:* Back in lecture 1, we saw that by using two's complement representation, we could perform subtraction using addition.

(B) Implement your subtractor as a Minispec function sub4. Your function can use at most one rca4 function (the function implementing 4-bit ripple carry adder we saw in lecture).

function Bit#(5) sub4(Bit#(4) a, Bit#(4) b); return real ( a, ~b, endfunction bina - 1 of 6 -L08 – Combinational Logic 1 6.004 Worksheet

#### Problem 2. **★**

X ( ) pythen

$\chi(3] + \chi(2) + \chi(1) + \chi(0)$

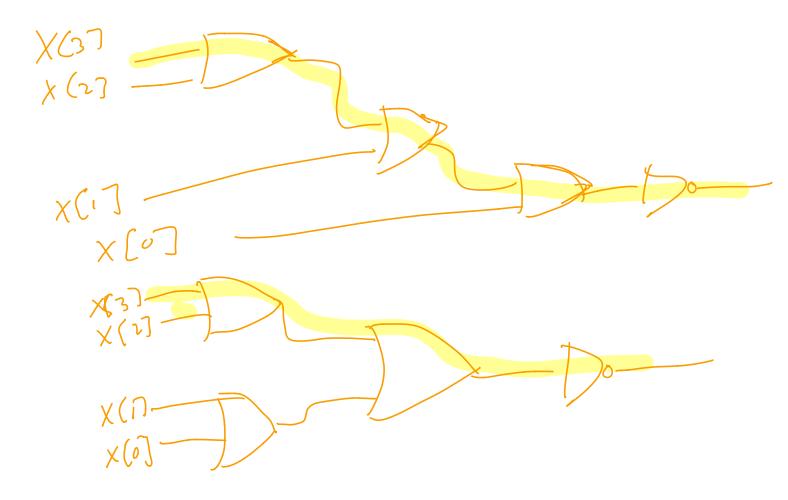

(A) Implement a Minispec function isZero that returns 1 if its 4-bit input is zero, and 0 otherwise. Your implementation can only use bitwise logical operations and bit selection, and cannot use the equality/inequality operators.

ion Bit#(1) isZero(Bit#(4) x);  $\chi(3) \times (27 \times 10^{-7})$   $N \in U \setminus V \setminus (3) = U \setminus (27 \times 10^{-7})$ endfunction de enis

function Bit#(1) isZero(Bit#(4) x);

(B) Manually synthesize your function into a combinational circuit using 2-input AND gates, 2input OR gates, and inverters. Keep delay low by minimizing the number of logic gates between input and output. Draw the resulting circuit.

# = 6x8 6x0008

### Problem 3. **★**

Write the truth table for the combinational device described by the function below.

$$function Bit#(2) f(Bit#(1) a, Bit#(1) b, Bit#(1) c);

Bit#(4) upper = 4'hB; // hex value 0xB

Bit#(4) lower = (c == 1)? 4'hB : 4'h7;

Bit#(2) ret = case (ta,b);

0 : 1;

1: x[1:0];

2: x[3:2];

3: x[7:6] ^ 2'b11; A = Ob/O!

endcase;

return ret;

b = 0b O!O

(A, b3)

= 0b [b! 0!b]

0 0 1

elx it  $\{a, b3 == 0$ ;

wetworn l

0 0 0

0 0 1

elx it  $\{a, b3 == 2$ ;

wetworn  $X(1:0]$

elx it  $\{a, b3 == 2$ ;

wetworn  $X(3:2]$

$1 0 1$

$1 0 0$

$1 1 1$

$1 0 0$

$1 1 1$

$1 0 0$

$1 1 1$

$1 0 0$

$1 1 1$

$1 0 0$

$1 1 1$

$1 1 0$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 0$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1$

$1 1 1 1$

$1$$$

6.004 Worksheet

net, and not Problem 4. Show that 1-bit 2-to-1 muxes are universal, i.e., they can be used to implement any combinational circuit. To show universality, implementing an inverter, an AND gate, and an OR gate using only 1-bit 2-to-1 muxes. You may tie inputs to 1 or 0 if necessary, and may use one or multiple muxes. Clearly label all inputs and outputs.  $rt \leq z = 1$ Z(A, B, S) $\mathbf{Z} = \mathbf{A} \cdot \mathbf{S} + \mathbf{B} \cdot \bar{\mathbf{S}}$ Ζ perunA B else H 5==0: return B NUT Logic diagram of inverter implementation using 2-input mux: 0 Logic diagram of AND gate implementation using 2-input mux  $2 = A \cdot S +$ AND (A,B)  $7 = A \cdot S$ () Z(A, 0, B) NOT Logic diagram of OR gate implementation using 2-input mux: 7(1, B, 5)Z=A. S+B.S  $Z = S + B \cdot S$ FOR = 5+B B Z(1, A,B, L08 – Combinational Logic 1 6.004 Worksheet - 4 of 6 -

depend on the input value?

### Problem 5.

0

6

The parity of an n-bit number x is 1 if x has an odd number of 1's, and 0 otherwise. Parity is useful to detect single-bit errors, as a single bit flip changes the parity of a value.

ß

21

'D,1,

(A) Write a Minispec function addParity that takes as input 4-bit value and returns a 5-bit output that adds a parity bit to the input in the most significant position. In other words, the most-significant bit of the output should be the input's parity, and the remaining bits should be the input.

D

B) What is the parity of the outputs of the addParity circuit? Does the parity of the output

(C) Write a Minispec function checkParity that takes as input a 5-bit value and returns True if the input has an even number of 1's, and returns False otherwise.

6.004 Worksheet

$(V \wedge v p(A, B)) = \mathcal{Z}(0, 1, \mathcal{Z}(A, 0, B))$

7, (0,1

2(1, 2(0, 1, A), 2(0, 1, B))

### Problem 6. Combinational Minispec (part of Spring 2020 Quiz 2 problem 3, 8 points)

Complete the truth table for the following Minispec function.

```

function Bit#(3) h(Bit#(1) a, Bit#(2) b);

Bit#(3) ret = 3'b110;

case ({a, b[1]})

0: ret = {1'b0, zeroExtend(a) & b};

1: ret = zeroExtend(a) + signExtend(b);

3: ret = {a, ~b};

default: ret = 3'b010;

endcase

return ret;

endfunction

```

| а | b[1] | b[0] | ret[2] | ret[1] | ret[0] |

|---|------|------|--------|--------|--------|

| 0 | 0    | 0    |        |        |        |

| 0 | 0    | 1    |        |        |        |

| 0 | 1    | 0    |        |        |        |

| 0 | 1    | 1    |        |        |        |

| 1 | 0    | 0    |        |        |        |

| 1 | 0    | 1    |        |        |        |

| 1 | 1    | 0    |        |        |        |

| 1 | 1    | 1    |        |        |        |

- 6 of 6 -

(Label: 3A) Copy the truth table and fill in all the missing blanks.